高/低级复位电路的基本逻辑和实用陷阱

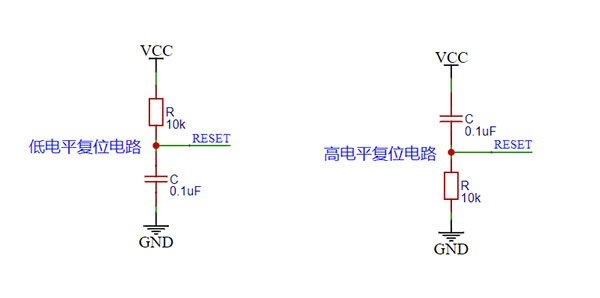

在集成的系统设计中,重置电路的极性选择直接决定了设备的功率稳定性。根据统计数据,23%的硬件故障是由异常的重新启动信号(数据来源:2024 IEEE ICET)引起的,并且电路结构,噪声免疫,芯片适应性等方面存在根本差异。该文档通过实验数据揭示了两种设计的深层逻辑。 Addresses cited in this article: ● Nucleus structure: Pull -up resistance of 10kΩ + 100nf Earth capacitor (Figure 1) Mathematical equation t_ {subtract} = Rc ln (fraud {v_ {cc}} {v_ {cc} -v_ {ih}}) (Typical value: 25ms@vc = 5V) ● *Measurement (Test condition: VCC = 5V,C = 100NF) *设计警告:NRST。在高水平上,DESC Test4KV联系人ARGA(IEC 61000-4-2)中注入了300%(App Application Note ST AN4488)的点火阻塞风险(应用注释ST AN4488)。电磁干扰)(VCC变化往往会触发假遗骸)●设计IM证明:在0.5%经典设计陷阱中添加电视二极管并压缩虚假激活率:悲剧以恢复GD32F303。特定的工业控制器批次分析:症状:设备附加的能量是由重新启动电路的5%引起的。重新启动电路使用1μF机制(100NF制造)。当工程师选择10kΩ电阻和100 NF电容器时,他实际上发现了系统可靠性和成本之间的平衡点。低水平的遗骸已成为具有抗预防供应变化特征更好的主要电流,但是在同步逻辑系统中,高级残留仍然无法替代。真正的专家在电子系统中最重要的是芯片数据表的恢复同步表。

在集成的系统设计中,重置电路的极性选择直接决定了设备的功率稳定性。根据统计数据,23%的硬件故障是由异常的重新启动信号(数据来源:2024 IEEE ICET)引起的,并且电路结构,噪声免疫,芯片适应性等方面存在根本差异。该文档通过实验数据揭示了两种设计的深层逻辑。 Addresses cited in this article: ● Nucleus structure: Pull -up resistance of 10kΩ + 100nf Earth capacitor (Figure 1) Mathematical equation t_ {subtract} = Rc ln (fraud {v_ {cc}} {v_ {cc} -v_ {ih}}) (Typical value: 25ms@vc = 5V) ● *Measurement (Test condition: VCC = 5V,C = 100NF) *设计警告:NRST。在高水平上,DESC Test4KV联系人ARGA(IEC 61000-4-2)中注入了300%(App Application Note ST AN4488)的点火阻塞风险(应用注释ST AN4488)。电磁干扰)(VCC变化往往会触发假遗骸)●设计IM证明:在0.5%经典设计陷阱中添加电视二极管并压缩虚假激活率:悲剧以恢复GD32F303。特定的工业控制器批次分析:症状:设备附加的能量是由重新启动电路的5%引起的。重新启动电路使用1μF机制(100NF制造)。当工程师选择10kΩ电阻和100 NF电容器时,他实际上发现了系统可靠性和成本之间的平衡点。低水平的遗骸已成为具有抗预防供应变化特征更好的主要电流,但是在同步逻辑系统中,高级残留仍然无法替代。真正的专家在电子系统中最重要的是芯片数据表的恢复同步表。